80386 Microprocessor is a 32-bit processor that holds the ability to carry out 32-bit operation in one cycle. It has data and address bus of 32-bit each. Thus has the ability to address 4 GB (or 232) of physical memory.

Multitasking and protection capability are the two key characteristics of 80386 microprocessor. 80386 has an internal dedicated hardware that permits multitasking.

This was 80386 microprocessor that was designed by Intel in October 1985 and was an upgraded version of 80286 microprocessor.

Features of 80386

- As it is a 32-bit microprocessor. Thus has 32-bit ALU.

- 80386 has data bus of 32-bit.

- It holds address bus of 32 bit.

- It supports physical memory addressability of 4 GB and virtual memory addressability of 64 TB.

- 80386 supports variety of operating clock frequency, which are 16 MHz, 20 MHz, 25 MHz and 33 MHz.

- It offers 3 stage pipeline: fetch, decode and execute. As it supports simultaneous fetching, decoding and execution inside the system.

Operating modes of 80386

We have already discussed in our previous article that 80286 supports two operating modes. The first is real address mode while the second is the protected virtual address mode. However, 80386 supports 3 operating modes: real, protected and virtual real mode.Of the two modes of 80286 microprocessor, initially the 80286 was booted in real mode. However, to have better operating performance, separate software command is used to switch from the real mode to the protected mode.

But it requires the resetting of microprocessor in order to switch to real mode from protected mode. This drawback was eliminated in 80386 that allows the switching between the modes using software commands.

In the protected mode, 80386 microprocessor operates in similar way like 80286, but offers higher memory addressing ability.

In virtual mode, the overall memory of 80386 can be divided into various virtual machines. And all of them acts as a separate computer with 8086 microprocessor. This mode is also called virtual 8086 mode or V86 mode.

The other one is the virtual real mode, this mode allows the system to execute multiple programs in the protected memory. And in case a program at a particular memory gets crashed then it will not cause any adverse effect on the other part of the memory.

Architecture of 80386 Microprocessor

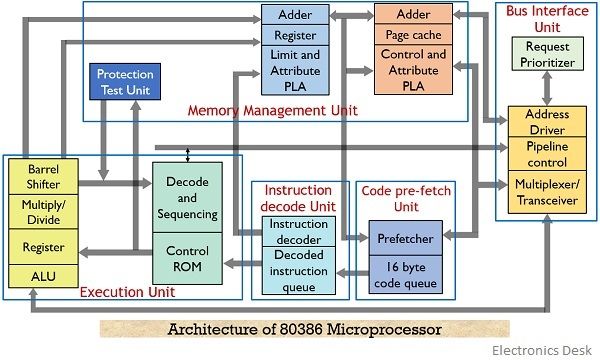

The figure below shows the architectural representation of 80386 microprocessor: Basically it has 6 functional units which are as follows:

Basically it has 6 functional units which are as follows:- Bus Interface Unit

- Code Fetch Unit

- Instruction Decode Unit

- Execution Unit

- Memory Management Unit

This pipelining technique leads to reduction in overall processing time thereby increasing the performance of the overall system.

Let us now move further and understand the operation of each unit in detail.

1. Bus Interface Unit

The bus interface unit or BIU holds a 32-bit bidirectional data bus as well as 32-bit address bus. Whenever a need for an instruction or a data fetch is generated by the system then the BIU generates signals (according to the priority) for activating the data and address bus in order to fetch the data from the desired address.The BIU connects the peripheral devices through the memory unit and also controls the interfacing of external buses with the coprocessors.

2. Code Prefetch Unit

This unit fetches the instructions stored in the memory by making use of system buses. Whenever the system generates a need for an instruction then the code prefetch unit fetches that instruction from the memory and stores it in 16-byte prefetch queue.So to speed up the operation this unit fetches the instructions in advance and the queue stores these instructions.

The sequence in which the instructions are fetched and gets stored in the queue depends on the order they exist in the memory.

As this unit fetches one double word in single access. So, in such a case, it is not necessary that each time only a single instruction will be fetched, as the fetched instruction can be parts of two different instructions.

It is to be noted here that, code prefetching holds lower priority than data transferring. As whenever, a need for data transfer is generated by the system then immediately the code prefetcher leaves the control over the buses. So that the BIU can transfer the required data.

But prefetching of instruction and storing it in the queue reduces the wait for the upcoming instruction to almost zero.

3. Instruction Decode Unit

We know that instructions in the memory are stored in the form of bits. So, this unit decodes the instructions stored in the prefetch queue. Basically the decoder changes the machine language code into assembly language and transfers it to the processor for further execution.4. Execution Unit

The decoded instructions are stored in the decoded instruction queue. So, these instructions are provided to the execution unit in order to execute the instructions.The execution unit controls the execution of the decoded instructions. This unit has a 32-bit ALU, that performs the operation over 32-bit data in one cycle. Also, it consists of 8 general purpose as well as 8 special purpose registers. These are used for data handling and calculation of offset address.

5. Memory Management Unit

This unit has two separate units within it. These are- Segmentation Unit and

- Paging Unit

It gives 4 level protection to the data or code present in the memory. Every information in the memory is assigned a privilege level from PL0 to PL3. Here, PL0 holds the highest priority and PL3 holds the lowest priority.

Suppose a file (either data or code) is needed to be accessed is stored in the memory at PL0. Then only those programs which are working at PL0 would be able to access that file. While other programs will not be able to access the same.

Also, if a file is present at PL1, then programs of PL0 and PL1 both can access it. As PL0 has higher priority than PL1. So, for protection purpose the main part of OS is stored in PL0 while PL3 holds the user programs.

Providing protection to the data or code inside the system is the most advantageous factor that was first given by 80386 microprocessor.

Paging Unit: The paging unit operates only in protected mode and it changes the linear address into physical address. As the programmer only provides the virtual address and not the physical address.

The segmentation unit controls the action of paging unit, as the segmentation unit has the ability to convert logical address into linear address at the time of executing an instruction.

Basically it changes the overall task map into pages and each page has a size of 4K. This allows the handling of task in the form of pages rather than segments.

Paging unit supports multitasking. This is so because the physical memory is not required to hold the whole segment of any task. Despite, only that part of the segment which is needed to be currently executed must be stored in that memory whose physical address is calculated by the paging unit.

This resultantly reduces the memory requirement and hence this frees the memory for other tasks. Thus by this we get an effective way for managing the memory to support multitasking.

This is all about the architecture of 80386 microprocessor.

A noteworthy point over here is that 80386 has 2 different versions. These are 80386SX and 80386DX. The SX stands for single execution while the DX stands for double execution.

80386SX holds a data bus of 16-bit. While 80386DX has a data bus of 32-bit.

Whenever we talk about 80386 then it nothing but 80386DX having 32-bit data bus. But sometimes a system having 8086 microprocessor needs to improve the its performance as well as protection. And we know that 8086 is a 16-bit microprocessor, that operates on 2 banks.

But 80386 in general has a 32-bit data bus that needs 4 banks. So, to access some of the features of 80386 in a system having 8086 processor, we use 80386SX as processor having data bus of 16-bit.

Thus in this case, a system can be upgraded to facilities of 80386 by simply changing the processor despite changing the overall system. This is reason why we have 80386SX version of the 80386 microprocessor.

Generally, we consider 80386 as 80386DX, a processor with 32-bit of data bus.

Source: https://electronicsdesk.com/80386-microprocessor.html

Post a Comment

Your feedback is welcome. Be it positive or negative. Please do not post any irrelevant comment or abuse anyway.